## PROVIDING PERFORMANCE GUARANTEES WITH CROSSBAR-BASED ROUTERS

#### A DISSERTATION

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING

AND THE COMMITTEE ON GRADUATE STUDIES

OF STANFORD UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

**DOCTOR OF PHILOSOPHY**

Shang-Tse Chuang

December 2004

UMI Number: 3153199

Copyright 2005 by Chuang, Shang-Tse

All rights reserved.

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

UMI Microform 3153199

Copyright 2005 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346 © Copyright by Shang-Tse Chuang 2005 All Rights Reserved

|  |  |  |   |         |        |       | f Doggo      |            |        |       | adequate |

|--|--|--|---|---------|--------|-------|--------------|------------|--------|-------|----------|

|  |  |  |   |         |        | 14    | 44           | D          |        |       |          |

|  |  |  | j | Prof. 1 | Nichol | as W. | ALA<br>McKed | 力<br>own l | Princi | pal A | dvisor   |

|  |  |  |   |         |        |       |              |            |        |       |          |

|  |  |  |   |         |        |       |              |            |        |       |          |

|  |  |  |   |         |        |       |              |            |        |       |          |

Prof. Balaji Prabhakar

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as dissertation for the degree of Doctor of Philosophy.

Prof. Ashish Goel

Approved for the University Committee on Graduate Studies

#### Abstract

The backbone of the Internet is comprised of a network of high performance routers. Every router receives packets and forwards them to the correct outgoing port. Routers are designed to achieve a specific capacity, and network operators expect routers to provide predictable performance. This thesis is about how to design practical routers with predictable performance.

Network operators expect certain performance characteristics; for example, if the arrival rate is less than the router's advertised capacity, they can reasonably assume the router can handle the traffic. Somewhat surprisingly, no commercial router can do this today. And some operators would like to provide customers with service guarantees such as guaranteed bandwidth and delay through their network. To provide these guarantees, each individual router within the network must also provide bandwidth and delay guarantees.

Most high performance routers built today use crossbars and a centralized scheduler. Building crossbar-based routers which provide these performance guarantees is difficult using current technology. Scheduling the crossbar is a bottleneck and limits scalability. It also makes it impractical to provide performance guarantees. As line rates and the number of ports increase, the scheduling problem will only become more difficult.

This thesis describes crossbar scheduling algorithms that provide deterministic throughput, bandwidth, and delay guarantees. Each technique is based on an analytical counting method. The first result — for crossbar switches — is primarily a theoretical observation of what is possible, but is too complex to be practical. To

make the result more practical, I describe crossbars with a small amount of internal buffering. A buffered crossbar simplifies the scheduling process and provides a practical way to build routers with performance guarantees.

## Acknowledgements

I am indebted to many for their advice and assistance throughout my time at Stanford.

First and foremost, I would like to thank my adviser, Nick McKeown, for his continued support, guidance, and encouragement in both academia and industry. Nick always has been able to bring out the best in people and has a great instinct to identify what matters most. I really appreciate all that you have taught me.

I am abundantly grateful to my co-advisor, Balaji Prabhakar, for his encouragement and most of all his advice. Thank you for always being there for me.

I would also like to thank Ashish Goel for the many discussions that led to a number of results in this thesis. I really appreciate the good times we spent together.

Numerous discussions with Sundar Iyer lead to most of the work on the buffered crossbar results. It has been a pleasure working with you.

Many people have greatly helped in the preparation of this thesis. I am especially grateful to Greg Watson and Isaac Keslassy for reviewing and providing feedback on the entire thesis. I would also like to acknowledge the helpful feedback from Midge Eisele, Nandita Dukkipati, Sundar Iyer, and Martin Casado.

My time at Stanford has been split into two fantastic periods. From the earlier period, I would like to thank the following group members for all the good times: Adisak, Jeff, Ken, Lorenz, Pablo, Rolf, Steve, and Youngmi. My thanks also go out to the following group members from the latter period: Gireesh, Greg, Guido, Isaac, Martin, Masayoshi, Matthew, Mingjie, Nandita, Pablo, Rui, Sundar, and Yashar.

I would also like to thank my family: my father Shinn-Fu, my mother Jen-Ian, my brother Ki and my sister Tian for always encouraging me to make the most out

of my life.

And most of all, I would like to thank my wife, Ingrid, for her unconditional support, encouragement, and patience. This thesis is dedicated to my loving wife.

## Contents

| $\mathbf{A}$ | bstra | act                    |                         |                                       |            | iv |

|--------------|-------|------------------------|-------------------------|---------------------------------------|------------|----|

| $\mathbf{A}$ | ckno  | $\mathbf{wledgements}$ |                         |                                       |            | vi |

| 1            | Int   | roduction              |                         |                                       |            | 1  |

|              | 1.1   | Performance Guarar     | ntees                   |                                       |            | 3  |

|              |       | 1.1.1 Throughput       | Guarantees              |                                       |            | 5  |

|              |       | 1.1.2 Bandwidth a      | nd Delay Guarantees     |                                       |            | 6  |

|              | 1.2   | Switch Architectures   | 5                       |                                       |            | 8  |

|              | 1.3   | Motivation of Thesis   | 3                       |                                       |            | 11 |

|              |       | 1.3.1 Minimum Sp       | eedup to Emulate an     | OQ Switch                             |            | 11 |

|              |       | 1.3.2 Emulating a      | PIFO OQ Switch          |                                       |            | 11 |

|              |       | 1.3.3 Providing En     | nulation in a Practical | Way                                   |            | 12 |

|              | 1.4   | Outline of Thesis .    |                         |                                       |            | 12 |

| 2            | Mir   | nicking an OQ Swi      | tch Using a Traditi     | onal Crossbar                         |            | 13 |

|              | 2.1   | Background             |                         | · · · · · · · · · ·                   |            | 14 |

|              | 2.2   | General Structure of   | Scheduling Algorithm    | as                                    |            | 15 |

|              | 2.3   | Definitions            |                         | · · · · · · · · · · · · · · · · · · · |            | 18 |

|              | 2.4   | Necessity and Suffici  | ency                    |                                       |            | 19 |

|              | 2.5   | A Simple Input Que     | ue Insertion Policy .   |                                       |            | 20 |

|              | 2.6   | Towards Making CC      | F Practical             |                                       |            | 22 |

|              |       | 2.6.1 The Delay Ti     | ill Critical (DTC) Stra | itegy                                 |            | 23 |

|              |       | 2.6.2 The Group B      | By Virtual Output Que   | eue (GBVOQ) A                         | lgorithm . | 24 |

|              | 2.7 Conclusions                                   |

|--------------|---------------------------------------------------|

| 3            | Buffered Crossbars                                |

|              | 3.1 Background                                    |

|              | 3.1.1 Why use Buffered Crossbars?                 |

|              | 3.2 Achieving 100% throughput                     |

|              | 3.3 Counting Method with a Buffered Crossbar      |

|              | 3.4 Rate Guarantees with a Buffered Crosbar       |

|              | 3.5 Delay Guarantees in a Buffered Crossbar       |

|              | 3.5.1 Delay guarantees with speedup three         |

|              | 3.5.2 Delay guarantees with speedup two           |

|              | 3.6 Conclusions                                   |

|              |                                                   |

| 4            |                                                   |

|              | 4.1 Router Design Using Buffered Crossbars        |

|              | 4.2 Future Research                               |

|              | 4.2.1 Larger Buffers per Crosspoint               |

|              | 4.2.2 100% Throughput with Larger Buffers         |

|              | 4.2.3 Variable Length Packets                     |

| $\mathbf{A}$ | Necessity and Sufficiency of a Speedup of $2-1/N$ |

|              | A.1 The Necessity of a Speedup of $2-1/N$         |

|              | A.2 The Sufficiency of a Speedup of $2-1/N$       |

|              |                                                   |

| В            | Acyclic Dependency Graph                          |

| $\mathbf{C}$ | Non-Negative Slackness with GBVOQ                 |

|              |                                                   |

| D            | Achieving 100% Throughput                         |

| $\mathbf{E}$ | Mimicking an OQ Switch                            |

|              | E.1 Mimicking a Restricted PIFO OQ Switch         |

|              | E.2 Mimicking an OQ Switch Using a WRR Policy     |

|              | E 3 Mimicking a PIFO OO Switch                    |

| F Buffered Cro | Buffered Crossbar with N Cells Per Output |  |  |  |    |  |  |  |  |

|----------------|-------------------------------------------|--|--|--|----|--|--|--|--|

|                |                                           |  |  |  |    |  |  |  |  |

| Bibliography   |                                           |  |  |  | 69 |  |  |  |  |

# List of Figures

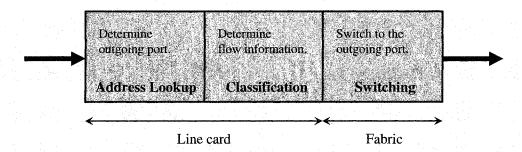

| 1-1 | Datapath of a packet through a flow-aware router                          | 2  |

|-----|---------------------------------------------------------------------------|----|

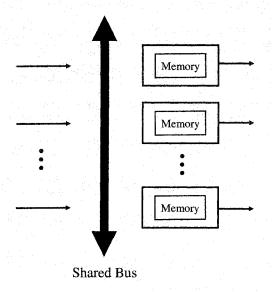

| 1-2 | Output Queued (OQ) Switch                                                 | 4  |

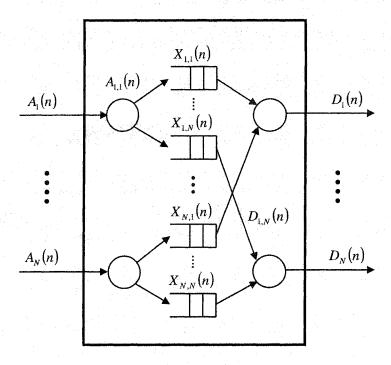

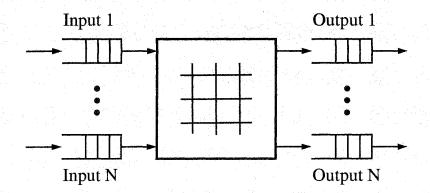

| 1-3 | A simple model of a generic switch with $N$ inputs and $N$ outputs        | 6  |

| 1-4 | A diagram of one output of an OQ switch using a weighted fair queue-      |    |

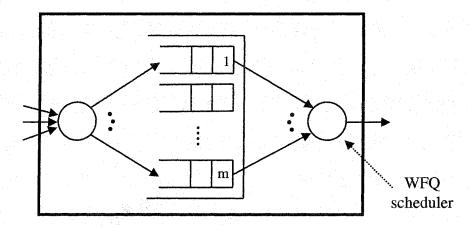

|     | ing (WFQ) scheduler                                                       | 7  |

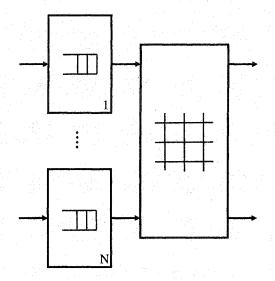

| 1-5 | An Input Queued (IQ) switch                                               | 8  |

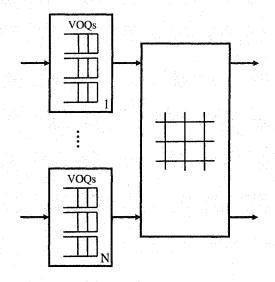

| 1-6 | An Input Queued (IQ) switch with Virtual Output Queues (VOQs)             | 9  |

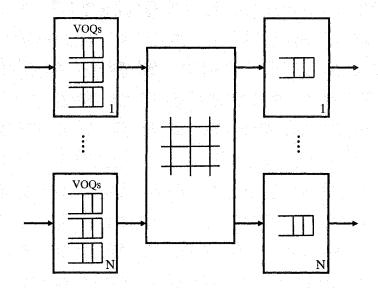

| 1-7 | A Combined Input Output Queued (CIOQ) switch with Virtual Out-            |    |

|     | put Queues (VOQs)                                                         | 10 |

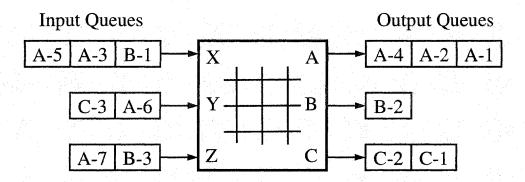

| 2-1 | A general Combined Input and Output Queued (CIOQ) switch                  | 14 |

| 2-2 | A snapshot of a CIOQ switch                                               | 19 |

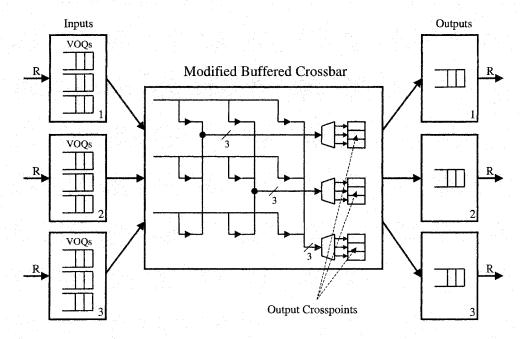

| 3-1 | The architecture of the buffered crossbar with three ports                | 28 |

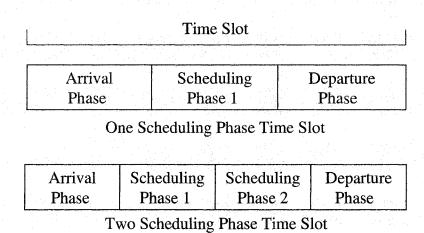

| 3-2 | The scheduling phases for the buffered crossbar                           | 30 |

| 3-3 | The insertion policy for achieving delay guarantees                       | 38 |

| 3-4 | The architecture of a modified buffered crossbar with three ports         | 40 |

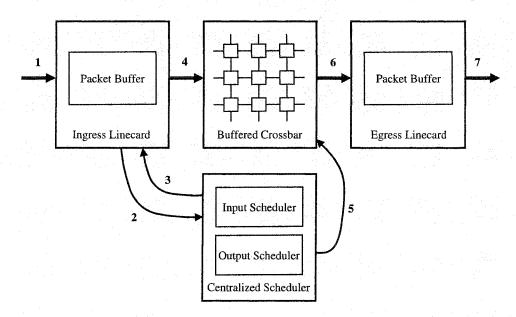

| 4-1 | Datapath of a packet through a router using a buffered crossbar           | 44 |

| A-1 | One scheduling phase and two scheduling phase time slots                  | 48 |

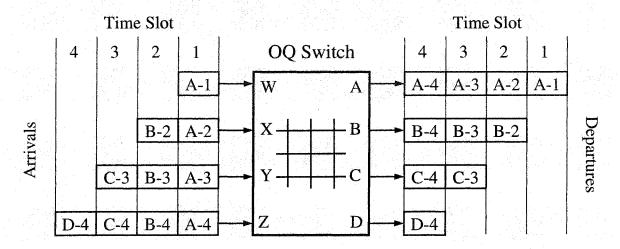

| A-2 | Lower bound input traffic pattern for a $4 \times 4$ switch               | 49 |

| A-3 | Scheduling order for the lower bound input traffic pattern in Figure A-2. | 49 |

## Chapter 1

#### Introduction

The Internet consists of end-hosts, links, and routers. This thesis is about the design and architecture of high performance Internet routers that make up the backbone of the Internet — in particular, how to design them to perform predictably and yet still be implementable.

A router consists of several processing stages. When designing a router to have predictable performance (we will explain below exactly what we mean by "predictable"), we need to make sure that each processing stage behaves predictably. At the very least, a router has two main processing stages: address lookup and switching. In the address lookup stage, the router examines the packet header to decide where the packet should be sent next. In the switching stage, the router transfers the packet to the correct outgoing port in preparation to depart. This thesis focusses on the switching stage of the router.

Some routers have more processing stages. For example, if a router provides bandwidth or delay guarantees to different packet flows, it needs to be "flow-aware" [1]. Flow-aware routers include firewalls, load-balancers, and routers that provide perflow delay and bandwidth guarantees. When a packet arrives to a flow-aware router, the router first has to decide which flow the packet belongs to. This is called *classification*. Usually, a packet is then buffered in a queue dedicated to its flow so that the packets within a flow are all treated the same way and are processed in FIFO order.

Figure 1-1 shows how a packet is processed by a flow-aware router from when it arrives on the ingress line until it departs on the egress line. The packet goes through

Figure 1-1: Datapath of a packet through a flow-aware router.

the following stages. In the address lookup stage, the router determines the outgoing port of the packet. Then, the router determines which flow the packet belongs to in the classification stage. In the switching stage, packets are segmented into cells, traverse the switch fabric as cells, and reassembled back into packets again before they leave the router.<sup>1</sup>

Network operators need to design and plan their networks. They know the capacity of the links, and they are told the capacity of the router. However, although they can use up to 100% of the links, it is perhaps surprising that they can not use up to 100% of the router capacity. A router's capacity depends on the arriving traffic patterns that expose imperfections in the router, such as blocking or inefficient scheduling algorithms. No commercial router today can guarantee that 100% of its capacity is available to the network operator. This makes it hard to plan a network—not just under normal operating conditions (when utilizations are typically low), but under failure conditions when traffic is rerouted and the utilization of links and routers grows. Put another way, when a network operator spends millions of dollars on a router for its backbone network, it seems reasonable to expect that one can use all of the router capacity, regardless of the arrival process of packets. In other words, as long as the router receives packets at a rate within its capacity, it should be able to fully utilize the links and, therefore, guarantee 100% throughput.

Furthermore, network operators want their networks to be designed to provide their customers with a number of service guarantees. These services (which are the

<sup>&</sup>lt;sup>1</sup>Although packets arriving to the router may have variable length, we will assume that they are treated internally as fixed-length *cells*. This is common in high performance routers [2, 3].

basis of Service Level Agreements (SLAs)) provide guaranteed bandwidth and delay through their networks. For example, large corporations might want to guarantee a fixed bandwidth between their company sites. Similarly, if a network operator can guarantee a maximum delay through their networks, they can also sell services to customers who run real-time applications such as video and voice. In order for a network to provide bandwidth and delay guarantees, each individual router within the network must also provide bandwidth and delay guarantees.

In summary, network operators want routers which provide throughput, bandwidth, and delay guarantees. However, most high performance routers built today use architectures based on crossbars; and building crossbar-based routers which provide these performance guarantees is difficult using current technology. The bottleneck that prevents routers from providing these guarantees is scheduling in the switching stage. A crossbar-based router requires a centralized scheduler to determine when cells are to traverse the switch fabric. As line rates and number of ports increase, due to growth of Internet traffic, the scheduling problem will only become more difficult. In this thesis, I will introduce a set of new scheduling algorithms that provide performance guarantees and simplify the scheduling process.

The remainder of the introductory chapter describes in detail the desired performance guarantees and gives an overview of switch architectures and previous work. Finally, the chapter describes the motivation of the thesis and outlines new algorithms and architectures presented later in this thesis.

#### 1.1 Performance Guarantees

Network operators would like to build their networks using routers that give performance guarantees. They want routers that provide throughput, bandwidth and delay guarantees. These guarantees are the same guarantees an output queued (OQ) switch (shown in Figure 1-2) can provide.

When a packet arrives at an OQ switch, it is immediately placed in a memory dedicated to its outgoing line, where it waits until it leaves the switch. The output chooses which packet to send next from among all the packets waiting to leave from

Figure 1-2: Output Queued (OQ) Switch

the output. Because nothing prevents an output from keeping the output line busy whenever it has a packet, we say the switch is "work conserving". A work conserving switch has the highest throughput of any switch because the output line cannot carry any higher workload. It also has the lowest expected packet delay because — on average — packets leave earlier in a work-conserving switch than in any other switch.<sup>2</sup>

It is also well known that an OQ switch can allocate bandwidth to different flows of packets using techniques such as weighted fair queueing (WFQ) [4, 5] and deficit round robin (DRR) [6]. Furthermore, with an appropriate scheduling algorithm and sufficient internal buffers, an OQ switch can control the delay of individual packets through the switch [4, 5].

<sup>&</sup>lt;sup>2</sup>If packets are all the same length, then a work-conserving switch with any service policy — such as FCFS — minimizes expected packet delay. If packets are of unequal length, then a specific work-conserving policy — such as shortest remaining processing time — minimizes expected packet delay.

#### 1.1.1 Throughput Guarantees

A generic switch with N inputs and N outputs is shown in Figure 1-3. Assume time is slotted into cell times.  $A_{i,j}(n)$  is the cumulative number of arrivals to input i of cells destined to output j at time n while  $A_i(n)$  is the aggregate number of arrivals to input i. During each cell time, at most one cell can arrive at each input.  $\lambda_{i,j}$  is the arrival rate of  $A_{i,j}(n)$ .  $D_{i,j}(n)$  is the cumulative number of departures from output j of cells that arrived from input i while  $D_j(n)$  is the aggregate number of departures from output j. Similarly, during each cell time, at most one cell can depart from each output.  $X_{i,j}(n)$  is the total number of cells from input i to output j still in the system at time n. The evolution of cells from input i to output j can be represented as

$$X_{i,j}(n+1) = X_{i,j}(n) + A_{i,j}(n) - D_{i,j}(n).$$

Let A(n) denote the vector of all arrivals  $\{A_{i,j}(n)\}$ , D(n) denote the vector of all departures  $\{D_{i,j}(n)\}$ , and X(n) denote the vector of the number of cells still in the system. With this notation, the evolution of the system can be described as

$$X(n+1) = X(n) + A(n) - D(n).$$

**Definition 1** An arrival process is said to be admissible when no input or output is oversubscribed, i.e., when  $\sum_i \lambda_{i,j} < 1$ ,  $\sum_j \lambda_{i,j} < 1$ ,  $\lambda_{i,j} \geq 0$ .

**Definition 2** Traffic is called independent and identically distributed (iid) if and only if:

- 1. Every arrival is independent of all other arrivals both at the same input and at different inputs.

- 2. All arrivals at each input are identically distributed.

**Definition 3** A switch is said to achieve 100% throughput if under any admissible iid traffic, for every  $\epsilon > 0$ , there exists B > 0 such that

$$\lim_{n \to \infty} \Pr\{\sum_{i,j} X_{i,j}(n) > B\} < \epsilon$$

Figure 1-3: A simple model of a generic switch with N inputs and N outputs.

**Definition 4** A switch is said to be work-conserving if whenever there is a cell in the system for an output, then that output must be busy.

In an OQ switch, an output can select any cell destined to that output to be placed on the outgoing line. Therefore, if an output selects a cell when any of the queues associated with that output is nonempty, an OQ switch is work-conserving. Note that when a switch is work-conserving, outputs are idle only if there are no cells in the system for that output. This is the busiest any system can be and therefore maximizes throughput and minimizes the number of cells stored in the switch. So a switch that is work-conserving also provides 100% throughput.

#### 1.1.2 Bandwidth and Delay Guarantees

Bandwidth and delay guarantees can be provided by implementing a weighted fair queuing (WFQ) scheduler in an OQ switch. Arriving packets are classified into flows and stored in per-flow queues. When a packet arrives, its finishing time is

Figure 1-4: A diagram of one output of an OQ switch using a weighted fair queueing (WFQ) scheduler.

calculated. Packets are then serviced by the weighted fair queueing scheduler in the order of their finishing times. This has been proved to guarantee that each packet will depart the switch by its assigned finishing time and therefore makes it possible to bound the delay of the packet through the switch. More information can be found in the following references [4, 5]. Figure 1-4 shows the usual way to represent an OQ switch that implements WFQ. Each output consists of many logical First-In-First-Out (FIFO) queues, one for each flow. The WFQ scheduler decides which packet to transmit next by considering the head-of-line packet in each FIFO, and choosing the one with the earliest finishing time.

For our purposes here, we are going to use a different way to represent an OQ switch that implements WFQ. Instead of one queue for each flow, we are going to represent the output using a single queue that we call a Push-In-First-Out (PIFO) queue. As we will see later, this turns out to be a useful and equivalent abstraction of WFQ, that is easier to analyze. We will use the PIFO queue in several of our results in this thesis.

A PIFO is a single queue of all packets waiting to depart from an output. When a new packet arrives for the output, it is "pushed-in" to some location in the queue. Once in the queue, the cell's relative ordering with packets already in the queue does not change; packets can not switch places. Of course, new packets can arrive

Figure 1-5: An Input Queued (IQ) switch.

later and get pushed-in ahead of (or behind) the packet. Packets can only depart from the head of line. Essentially, when a packet arrives, the WFQ scheduler picks its departure order relative to other packets already in the output. In this way, a WFQ scheduler with a PIFO queue is exactly equivalent to a WFQ scheduler with per-flow FIFO queues. By selecting the finishing times of packets as before, an OQ switch using a PIFO queueing policy per output can provide bandwidth and delay guarantees. Furthermore, the PIFO model includes several other queueing policies such as weighted round-robin and strict priorities. For an OQ switch, each output maintains a queue for the cells waiting to depart the switch. A single PIFO queue can be used to model this by arranging the cells in the queue based on the departure order of the cells.

#### 1.2 Switch Architectures

An OQ switch can behave as well as an ideal router and provides the best performance guarantees; however, an OQ switch is impractical for high performance routers since the memory bandwidth of a  $N \times N$  OQ switch must run N times as fast as the line rate. Unfortunately, with high line rates, memories with sufficient bandwidth are

Figure 1-6: An Input Queued (IQ) switch with Virtual Output Queues (VOQs).

simply not available.

On the other hand, an input queued (IQ) switch shown in Figure 1-5 needs memory to run only as fast as the line rate. This makes input queueing very appealing for switches with fast line rates or with a large number of ports. For this reason, the highest performance switches and routers use input-queued (IQ) switches [2, 3]. However, IQ switches which use a single FIFO queue can suffer from head-of-line (HOL) blocking which occurs if the head-of-line cell blocks cells destined for a different output to be scheduled. This phenomenon can have a severe effect on throughput. It is well known that if each input maintains a single FIFO, then HOL blocking can limit the throughput to just 58.6% [7].

Fortunately, HOL blocking can be removed by using a simple buffering strategy at each input. Rather than maintain a single FIFO queue for all cells, each input maintains a separate FIFO queue for each output [8, 9, 10] as shown in Figure 1-6. This queueing discipline is often referred to as virtual output queueing (VOQ). HOL blocking does not occur because a cell cannot be blocked by a cell queued ahead of it that is destined for a different output. Furthermore, no additional speedup is required because at most one cell can arrive and depart from each input in a cell time. It has been shown that using a maximum weight matching algorithms such as MWM [9],

Figure 1-7: A Combined Input Output Queued (CIOQ) switch with Virtual Output Queues (VOQs).

OCF [11], or LPF [12], a switch using VOQs can achieve 100% throughput. However, these algorithms are too complex and are hard to implement in practice.

One method that has been proposed to increase performance is to increase the "speedup" of a switch. A switch with a speedup of S can remove up to S packets from each input and deliver up to S packets to each output within a time slot, where a time slot is the time between packet arrivals at input ports. Hence, an OQ switch must have a speedup of N whereas an IQ switch may have a speedup of one. For values of S between 1 and N, packets need to be buffered at the inputs before switching as well as at the outputs after switching. We call this architecture a combined input and output queued (CIOQ) switch shown in Figure 1-7.

Both analytical and simulation studies of a CIOQ switch which maintains a single FIFO at each input have been conducted for various values of speedup [13, 14, 15, 16]. A common conclusion of these studies is that with a speedup of four to five one can achieve about 99% throughput when arrivals are independent and identically distributed at each input and when the distribution of packet destinations is uniform across the outputs. However, not only do these studies consider only average delay

(and simplistic input traffic patterns), they also make no guarantees about the delay of individual packets. This is particularly important if a router is to offer QoS guarantees.

#### 1.3 Motivation of Thesis

We believe that a well-designed network switch should perform predictably in the face of all types of arrival process and allow the delay of individual packets to be controlled. So instead of finding values of speedup that work well on average or with simplistic and unrealistic traffic models, we want to figure out how a CIOQ switch mimics an OQ switch for all types of traffic. (Here, "mimics" means that when the same inputs are applied to both the OQ switch and our crossbar-based switch, the corresponding output processes from the two switches are completely indistinguishable.) This thesis solves problems associated with designing a CIOQ switch that mimics an OQ switch.

#### 1.3.1 Minimum Speedup to Emulate an OQ Switch

The approach of mimicking an OQ switch was first formulated in [17]. They showed that a CIOQ switch with a speedup of four can mimic a FIFO OQ switch for arbitrary input traffic patterns and switch sizes using an algorithm called Most Urgent Cell First Algorithm (MUCFA). Is there a speedup smaller than four that also provides the same behavior? Our objective is to find the minimum speedup required for a CIOQ switch to mimic an OQ switch.

#### 1.3.2 Emulating a PIFO OQ Switch

In [17], it was shown that mimicking a FIFO OQ switch was achievable. A FIFO OQ switch is work-conserving, but does not provide delay guarantees. An OQ switch that employs a PIFO model such as WFQ can provide delay guarantees. Therefore, another problem is to find an algorithm that allows a CIOQ switch to mimic a PIFO OQ switch.

#### 1.3.3 Providing Emulation in a Practical Way

The MUCFA algorithm requires a speedup of four and is too complex to implement in practice. A centralized location was required to keep track of the exact departure time of each cell in the system. Without finding a practical algorithm, mimicking an OQ switch is only theoretically interesting. Another problem we solve in this thesis is to find practical methods to mimic an OQ switch.

#### 1.4 Outline of Thesis

This thesis explains how to design a router to achieve the same throughput, bandwidth, and delay guarantees as an ideal OQ router. In Chapter 2, we present an analytical counting method that can be used to show how a CIOQ switch using a traditional crossbar can mimic an OQ switch. Running at a speedup of two, we show how cell scheduling on a traditional crossbar can theoretically mimic an OQ switch with delay guarantees. We will then discuss the communication complexity and describe how it is impractical for implementation.

In Chapter 3, we introduce a crossbar with a small amount of internal buffering. We will show how the counting method can also be applied on a CIOQ switch using a buffered crossbar to achieve the same behavior while simplifying the scheduling process. The key to the buffered crossbar is to allow inputs and outputs to schedule independently and in parallel. We will also show how a buffered crossbar running at a speedup of two can achieve 100% throughput and mimic an OQ switch with a distributed algorithm. We will also introduce a novel mechanism called header scheduling which allows a buffered crossbar running at a speedup of two to mimic an OQ switch with delay guarantees.

In the concluding chapter, we will suggest how to implement a router which achieves the same throughput, bandwidth, and delay guarantees as an ideal router. The proposed architecture incorporates the practical benefits of a buffered crossbar and provides a simple path to scale crossbar-based routers.

## Chapter 2

# Mimicking an OQ Switch Using a Traditional Crossbar

In this chapter, we show that a CIOQ switch with a speedup of two can behave identically to an OQ switch. The result holds for switches with an arbitrary number of ports and for any traffic arrival pattern. This result is also found to be true for a broad class of widely used output link scheduling algorithms such as weighted fair queueing, strict priorities, and FIFO. We introduce some specific scheduling algorithms that achieve this result. We also show more generally that a speedup of 2 - 1/N is both necessary and sufficient for a CIOQ switch to mimic a FIFO OQ switch.

It is worth briefly considering the implications of this result. It demonstrates that it is possible to mimic an  $N \times N$  OQ switch using buffer memory operating at only twice the speed of the external line. Previously, an OQ switch could only be implemented with memories operating at N times the speed of the external line. However, the advantages do not come for free. In essence, the memory bandwidth is reduced at the expense of a fast cell scheduling algorithm that is required to configure the crossbar. As we shall see, the scheduling algorithms are complex and not yet practicable to mimic fast OQ switches with a large number of ports. While we propose some strategies in this chapter, the later chapters provide a more practical solution.

Figure 2-1: A general Combined Input and Output Queued (CIOQ) switch

#### 2.1 Background

Consider the single stage,  $N \times N$  switch shown in Figure 2-1. Throughout this thesis we assume that the switch is empty before time t=1. The switch is said to have a speedup of S if it can remove up to S cells from each input and transfer at most S cells to each output in a time slot. A speedup of S requires the switch fabric to run S times as fast as the input or output line rate. For 1 < S < N buffering is required both at the inputs and at the outputs and leads to a combined input and output queued (CIOQ) architecture. We wish to solve the following problem:

The speedup problem: Determine the smallest value of S and an appropriate cell scheduling algorithm  $\pi$  that

- 1. allows a CIOQ switch to exactly mimic the performance of an output-queued switch (in a sense that will be made precise),

- 2. achieves this for any arbitrary input traffic pattern, and

- 3. is independent of the switch size.

We will require that any solution of the speedup problem provides the following feature: a CIOQ switch must behave identically to an OQ switch in the following sense:

**Definition 5 : Identical Behavior** -A CIOQ switch is said to mimic an OQ switch if, under identical inputs, the departure time of every cell from both switches is identical.

As a benchmark with which to compare our CIOQ switch, we will assume that there exists a shadow  $N \times N$  OQ switch that is fed the same input traffic pattern as the CIOQ switch. Our goal is to arrange for each cell to depart from the CIOQ switch at exactly the same time as its counterpart cell departs from the OQ switch. In the CIOQ switch, the sequence in which cells are transferred from their input queues to the output queue is determined by a scheduling algorithm. In each time slot, the scheduling algorithm matches each non-empty input with at most one output and, conversely, each output is matched with at most one input. The matching is used to configure the traditional crossbar fabric before cells are transferred from the input side to the output side. A CIOQ switch with a speedup of S is able to make S such transfers during each time slot.

Selecting the appropriate scheduling algorithm is the key to making a CIOQ switch mimic its shadow OQ switch. In order to provide identical behavior, a cell must be transferred to the output of the CIOQ switch before the departure time of the counterpart cell in the OQ switch. If the cell is prevented from reaching its output in time, the departures from both switches are not identical, and we will fail to mimic the shadow OQ switch.

### 2.2 General Structure of Scheduling Algorithms

For most of this thesis, we break each time slot of a CIOQ switch with a speedup of S into the following three phases:

- The Arrival Phase All arrivals of new cells to the input ports take place during this phase.

- The Scheduling Phases The scheduling algorithm selects cells to transfer from inputs to outputs and then transfers them across the crossbar. With a speedup of S, the scheduling algorithm makes S crossbar configurations.

- The Departure Phase All departures of cells from the output ports take place during this phase.

The order in which the three phases occur is not crucial to our algorithms. However, we shall use the above ordering as it makes our proofs simpler.

A *matching* of input ports to output ports is a set of cells waiting on the input side such that all these cells can be sent across the crossbar in a single transfer. During each scheduling phase the scheduler finds a *stable* matching between the input ports and the output ports.

In order to find a stable matching, it is assumed that each input of the CIOQ switch maintains a priority list, which can be thought of as an ordered set of cells waiting at the input port. A cell can be prevented from reaching its output on time by other cells at its input with a higher priority. The more cells ahead of it in the priority list, the longer it might take to be transferred to the output. Many orderings of the cells are possible — each ordering leading to a different scheduling algorithm, as we shall see.

Each output maintains a queue for the cells that have been transferred from the inputs and that are waiting to depart from the switch. In addition, each output also maintains an output priority list, an ordered list of cells at the inputs waiting to be transferred to this particular output. The output priority list is constructed based on the order in which the cells would depart from the OQ switch we wish to mimic, i.e., the shadow OQ switch. This priority list will depend on the queueing policy such as WFQ, strict priorities, FIFO, etc., followed by the OQ switch.

**Definition 6: Stable Matching** - A matching of input ports to output ports is said to be stable if for each cell c waiting in an input queue, one of the following holds:

- 1. Cell c is part of the matching; i.e., c will be transferred from the input side to the output side during this scheduling phase.

- 2. A cell that is ahead of c in its input priority list is part of the matching.

- 3. A cell that is ahead of c in its output priority list is part of the matching.

Notice that conditions 2 and 3 above may be simultaneously satisfied, but condition 1 excludes the other two. The conditions for a stable matching can be achieved using the so-called *stable marriage problem*. Solutions to the stable marriage problem are called stable matchings and were first studied by Gale and Shapley [18]; they gave

an algorithm that finds a stable matching in at most M iterations, where M is the sum of the lengths of all the input priority lists.

Our specification of the scheduling algorithm for a CIOQ switch is almost complete: the only thing that remains is to specify how the input queues are maintained. Different ways of maintaining the input queues result in different scheduling algorithms. In fact, the various scheduling algorithms presented later differ only in the ordering of the cells in their input queues. For reasons that will become apparent, we restrict ourselves to a particular class of orderings, which is defined as follows:

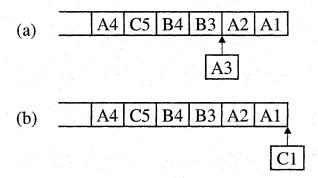

**Definition 7: Input Priority List Ordering** – When a cell arrives, it is given a priority number that dictates its position in the list; i.e., a cell with priority number X is placed at location  $(X+1)^{th}$  from the head of the list. A cell is placed in an input priority list according to the following rules:

- 1. Arriving cells are placed at an arbitrary location in the list,

- 2. The relative ordering of cells in the list does not change once cells are in the list, i.e., cells in the list cannot switch places, and

- 3. Cells may be selected to depart from the list from any location.

Thus, to complete our description of the scheduling algorithms, we only need to specify an insertion policy which determines where an arriving cell gets placed in its input priority list.

On the output side, the CIOQ switch keeps track of the departure order of each waiting cell. During each time slot the cell that departs from an output and is placed onto the outgoing line is the one with the earliest departure order. For the CIOQ switch to successfully mimic the shadow OQ switch, we must ensure that each cell crosses over to the output side before it is time for the cell to leave.

Even before we finish defining the algorithm, we can already see that it must maintain a large amount of state. More importantly, the algorithm must keep track of a large amount of *global* state, taking into account information about the queues at all the inputs and all the outputs. We will discuss in Section 2.6 the information complexity of these algorithms, and the difficulty of implementing them at high speed.

#### 2.3 Definitions

Based on the input and output priority lists, we can describe the following definitions that are crucial to the rest of the thesis.

**Definition 8 : Output Cushion** — At any time, the output cushion of a cell c, OC(c), is the number of cells waiting in the output buffer at cell c's output port with an earlier departure order than cell c.

Notice that if a cell is still on the input side and has a small (or zero) output cushion, the scheduling algorithm must urgently deliver the cell to its output so that it may depart on time. Since the switch is work-conserving, a cell's output cushion decreases by one during every time slot, and can only be increased by newly arriving cells that are destined to the same output with an earlier departure order.

**Definition 9 : Input Thread** — At any time, the input thread of cell c, IT(c), is the number of cells ahead of cell c in its input priority list.

In other words, IT(c) represents the number of cells currently at the input that need to be transferred to their outputs more urgently than cell c. A cell's input thread is decremented only when a cell ahead of it is transferred from the input and is possibly incremented by newly arriving cells. Notice that it would be undesirable for a cell to simultaneously have a large input thread and a small output cushion — the cells ahead of it at the input may prevent it from reaching its output before its departure time. This motivates our definition of slackness.

**Definition 10 : Slackness** – At any time, the slackness of cell c, L(c), equals its output cushion minus its input thread; i.e., L(c) = OC(c) - IT(c).

Slackness is a measure of how large a cell's output cushion is with respect to its input thread. If a cell's slackness is small, then it urgently needs to be transferred to its output. Conversely, if a cell has a large slackness, then it may languish at the input without fear of missing its departure time. Our approach will be to find

<sup>&</sup>lt;sup>1</sup>Note that a cell's input thread and slackness are only defined when the cell is waiting at the input side of the switch.

Figure 2-2: A snapshot of a CIOQ switch

scheduling algorithms for which the slackness is always non-negative. Although not strictly necessary, this will ensure that when a cell is transferred to the output its output cushion is non-negative. The idea is that when a cell's output cushion reaches zero, the cell's input thread must also equal zero. This means either: (1) that the cell is already at its output, and will depart the output on time, or (2) that the cell is at the head of its input priority list (because its input thread is zero), and will be transferred to the output immediately, which ensures that the cell will depart the output on time.

Figure 2-2 shows a snapshot of a CIOQ switch with a number of cells waiting at its inputs and outputs. For convenience we assume the time the snapshot was taken to be 1. Let P-t denote a cell that, in the shadow switch, will depart from output port P at time t. Consider, for example, the cell c denoted in the figure by A-3. For the CIOQ switch to mimic the shadow OQ switch, the cell must depart from port A at time 3. Its input thread is IT(c) = 1, since B-1 is the only cell ahead of c in the input priority list. Its output cushion is OC(c) = 2, since out of the three cells queued at A's output buffer, only two cells A-1 and A-2 will depart before it. Further, the slackness of cell c is given by L(c) = OC(c) - IT(c) = 1.

#### 2.4 Necessity and Sufficiency

Having defined the general structure of the scheduling algorithms, we now address the next natural question: what is the minimum required speedup, S, for a CIOQ

switch to mimic an OQ switch. The following theorem answers this question.

**Theorem 1** (Necessity). An  $N \times N$  CIOQ switch needs a speedup of at least 2-1/N to mimic an  $N \times N$  FIFO OQ switch.

Proof: The proof is by counter-example and is presented in Appendix A.1. ■ Remark: Since FIFO is a special case of a variety of output queueing disciplines, e.g., weighted fair queueing, strict priorities, etc., the lower bound applies to these queueing disciplines as well.

**Theorem 2** (Sufficiency). An  $N \times N$  CIOQ switch with a speedup of 2-1/N can mimic an  $N \times N$  FIFO OQ switch.

*Proof:* The proof is based on an insertion policy that we call Last In Highest Priority (LIHP) and is presented in Appendix A.2.

# 2.5 A Simple Input Queue Insertion Policy for a Speedup of 2

The proof of Theorem 2 is based on the LIHP input queue insertion policy and is, unfortunately, complex and somewhat counterintuitive. Further, LIHP is complex to implement, making it of little practical value. So in an attempt to provide a more intuitive understanding of the speedup problem, we present a simple and slightly more practical insertion policy that, with a speedup of two, mimics an OQ switch with a PIFO queueing discipline. We call this insertion policy Critical Cells First (CCF). As shown in the introduction, the broad class of PIFO queueing policies includes widely-used queueing policies such as WFQ and strict priority queueing. Notice that with an arbitrary PIFO policy, the departure time of a cell never decreases, but may increase because of the arrival of higher priority cells.

Recall that to specify a scheduling algorithm for a CIOQ switch, we simply need to give an insertion policy for the input queues. Critical Cells First (CCF) inserts an

arriving cell as far from the head of its input queue as possible, such that the input thread of the cell is not larger than its output cushion. More formally:

The CCF Insertion Policy: Suppose cell c arrives at input port P. Let X be the output cushion of c. Insert cell c into the  $X + 1^{th}$  position from the front of the input priority list at P. Hence, upon arrival cell c has a slackness of zero. If the size of this list is less than X cells, then place c at the end of the input priority list at P. Therefore, in this case, c has a positive slackness.

A consequence of CCF is that the slackness of a cell is always non-negative upon arrival. The intuition behind this insertion policy is that a cell with a small output cushion needs to leave soon (i.e., it is more critical) and therefore needs to be delivered to its output sooner than a cell with a larger output cushion. In other words, a cell with a large output cushion can safely reside further from the head of its input queue.

We now prove that CCF with a speedup of two mimics an OQ switch. Informally, the proof proceeds as follows. We first show a property of the CCF algorithm: that a cell never has a negative slackness, i.e., the input thread of a cell never exceeds its output cushion. We then proceed to show how this ensures that a cell always reaches the output side in time to leave.

**Lemma 3** The slackness L(c) of a cell c waiting on the input side is non-decreasing from time slot to time slot.

Proof: Let the slackness of a cell c be L(c) at the beginning of a time slot. During the arrival phase, the input thread of c can increase by at most one because an arriving cell might be inserted ahead of c in its input priority list. During the departure phase, the output cushion of c decreases by one. Now consider what happens in a scheduling phase. If c is scheduled in a scheduling phase, then it is delivered to its output and we no longer need to concern ourselves with c. If c is not scheduled, either a cell ahead of c in its input priority list or a cell ahead of c in its output priority list is scheduled (by the property of stable matchings, see Definition 6). Therefore, during a scheduling phase, either the input thread of c decreases by one, or the output cushion of c increases by one. The slackness of c, therefore, increases by at least one during each scheduling phase. Counting the changes in each of the three phases

(arrival, departure, and two scheduling phases), we conclude that the slackness of cell c cannot decrease from time slot to time slot.

Corollary 4 The slackness L(c) of a cell c is always non-negative.

*Proof:* Since the slackness of an arriving cell is non-negative due to the CCF insertion policy, it follows from Lemma 3 that the slackness of a cell is always non-negative.

**Theorem 5** Regardless of the incoming traffic pattern, a CIOQ switch that uses CCF with a speedup of 2 mimics a PIFO OQ switch.

**Proof:** Suppose that the CIOQ switch has successfully mimicked the OQ switch up until time slot t-1, and consider the beginning (first phase) of time slot t. We must show that any cell reaching its departure time is either: (1) already at the output side of the switch or (2) will be transferred to the output during time slot t. From Corollary 4, we know that a cell always has a non-negative slackness. Therefore, when a cell reaches its time to leave (i.e., its output cushion has reached zero), the cell's input thread must also equal zero. This means either: (1) that the cell is already at its output and may depart on time or (2) that the cell is simultaneously at the head of its input priority list (because its input thread is zero) and at the head of its output priority list (because it has reached its departure time). In this case, the stable matching algorithm is guaranteed to transfer it to its output during the time slot, and therefore the cell departs on time.

### 2.6 Towards Making CCF Practical

CCF as presented above suffers from two main disadvantages. First, the stable matching that we need to find in each scheduling phase can take as many as M iterations, where M is the sum of the lengths of all the input priority lists. Second, the algorithm has a high information complexity — CCF needs to know both the output cushion and departure order of each cell at the inputs, information that is not locally available at each input, but depends on the state of all the switch outputs.

We address these disadvantages in this section. The Delay Till Critical (DTC) strategy reduces the number of iterations needed to compute a stable matching to N; and the Group By Virtual Output Queue (GBVOQ) algorithm can mimic FIFO OQ switches without using global information. Unfortunately, combining the solutions does not help, i.e., we can reduce either the number of iterations to N or reduce the information complexity, but not both at the same time using these algorithms.

#### 2.6.1 The Delay Till Critical (DTC) Strategy

The Delay Till Critical strategy is as follows: During each scheduling phase, mark as "active" all cells with a slackness of zero and mark all other cells as inactive. The stable matching algorithm now considers only active cells. Intuitively, cells with zero slackness are the most critical and should be considered for immediate transfer across the fabric. Since the slackness of a cell can never become negative, CCF combined with DTC strategy can mimic any OQ switch that follows a PIFO queueing policy.

We will show that this simple strategy reduces the number of iterations required to compute a stable matching to N. Before we prove this fact, let us examine the problem that we are trying to remove. At any time instant, we define the dependency graph G to be a directed graph with a vertex corresponding to each active cell that is waiting on the input side of the CIOQ switch. Let a and b be two cells waiting at the input side. There is a directed edge from b to a if and only if cell a is ahead of b either in an input priority list or in an output priority list. Clearly two cells have to share either the same input port or the same output port if there is to be an edge between them. If we use CCF as defined in Section 2.5, there may be cycles in this dependency graph. These cycles are the main cause of inefficiency in finding stable matchings, and the DTC strategy is designed to remove these cycles.

**Lemma 6** If DTC is used in conjunction with CCF then, during any scheduling phase, the dependency graph is acyclic.

<sup>&</sup>lt;sup>2</sup>As soon as the slackness becomes zero, the cell would be marked active and the slackness would increase by one during the current scheduling phase (see Lemma 3). To prevent the slackness of a cell from decreasing by two before the next scheduling phase, we assume that the departure phase occurs before the second scheduling phase.

We defer the proof of Lemma 6 to Appendix B and instead focus on its implications, and how a match can be constructed in N iterations. First, let us consider how the first cell in the match is found. Since there are no cycles in G, there has to be at least one "sink" (i.e., a cell with no outgoing edges). Let cell c be the sink. Since there are no active cells ahead of c in either its input priority list or its output priority list, cell c has to be part of any stable matching of active cells. Hence c is guaranteed to be transferred to the output side, and therefore we can remove from the graph all cells which have the same input or output port as c; they clearly cannot be part of the match. The resulting graph is again acyclic, and we can repeat the above procedure N-1 more times to obtain a stable matching. Notice that each iteration of the above N iteration algorithm is quite straightforward.

We now address the second disadvantage of CCF, i.e., that of high information complexity.

# 2.6.2 The Group By Virtual Output Queue (GBVOQ) Algorithm

With CCF, the stable matching algorithm needs to calculate both the departure order and output cushion of each cell in the input queues. These quantities require centralized information about the state of all the queues in the system, making CCF (as described) unsuitable for a distributed implementation. However, for mimicking a FIFO OQ switch, we can group incoming cells into Virtual Output Queues and obtain an upper bound of N on the number of cells that need to be considered from each input. GBVOQ, the algorithm which achieves this bound, is described below.

At each input, GBVOQ maintains a single priority list as before, as well as a VOQ for each output port. All cells belong to a VOQ and to the single input priority list. When a new cell arrives, it is always placed at the tail of the corresponding VOQ. If the VOQ is empty, the new cell is placed at the head of the input priority list. If, on the other hand, the VOQ is non-empty, the new cell is inserted in the input priority list just behind the last cell belonging to the same VOQ; i.e., all cells that are in the same VOQ occupy contiguous positions in the input priority list. Therefore, to make

a scheduling decision, it is sufficient to only keep track of the relative priority ordering of VOQs. Since there are at most N VOQs at an input port in a FIFO switch, the size of the input priority list is bounded. The following lemma, which is proved in Appendix C, shows that GBVOQ assigns a non-negative slackness to an incoming cell.

**Lemma 7** The slackness L(c) of a newly arriving cell c is non-negative using the GBVOQ algorithm.

From Lemma 7, a CIOQ switch that uses GBVOQ with a speedup of two successfully mimics a FIFO OQ switch. At first glance, this insertion policy seems unfair. However, when a cell arrives to an empty VOQ, it is possible that there are no other cells in the system destined to that output. Therefore, the cell must immediately be transferred to the output in order to keep that output busy. The above insertion policy is designed to take care of this case.

Apart from small priority lists, GBVOQ has other desirable properties. First, the decision of where an incoming cell needs to be inserted is much simpler for GBVOQ than CCF — each input port can maintain its local priority queue without any access to global information. Second, during the stable matching phase, to determine which of two cells has a higher output priority, we only need to compare the arrival timestamps of the two cells. The cell which arrived earlier will have a smaller departure order (and hence a higher output priority) because of the FIFO property.

However, GBVOQ requires up to  $N^2$  iterations. The reason is that if two cells at the same input port are destined to the same output port, the one with the earlier departure order occurs ahead of the other in both the input and output priority list. Therefore, only the cell at the head of a VOQ needs to be considered. The DTC strategy cannot be applied to GBVOQ since to determine if a cell needs to be marked active, we again need access to global state, namely the output cushion of each cell at the head of a VOQ. Finding a solution which simultaneously has low information complexity and low number of iterations is a problem solved in the next chapter.

#### 2.7 Conclusions

We have seen that a CIOQ switch with a speedup of just two can behave identically to an OQ switch which employs a wide variety of packet scheduling algorithms such as WFQ, strict priorities, etc. Perhaps more importantly, we show this to be true for any traffic arrival pattern and for arbitrary switch sizes.

However, while this result makes possible a significant reduction in memory bandwidth, it comes at the expense of a scheduling algorithm. The scheduling algorithm is required to configure the crossbar, operating at least twice as fast as cells can arrive. While the algorithms that we describe here are quite simple, they require a stable matching of up to at least N iterations making them unsuitable for fast switches with a large number or ports. The result does not, however, preclude algorithms that are more readily implemented at higher speed. In the next chapter, we describe how a buffered crossbar, i.e., a crossbar with a small amount of internal buffering, can reduce this scheduling complexity.

## Chapter 3

### **Buffered Crossbars**

In the previous chapter, it was shown that a CIOQ switch using a traditional unbuffered crossbar with a speedup of two can mimic any PIFO OQ switch. However, the scheduling algorithms require high communication overhead and a large number of iterations making them impractical for fast OQ switches with a large number of ports.

In this chapter, we show how a buffered crossbar, i.e., a crossbar with a small amount of internal buffering, running at a speedup of two can also behave identically to an OQ switch. The scheduler for a buffered crossbar allows inputs and outputs to schedule independently and in parallel making it much simpler and, therefore, more practical than for a traditional unbuffered crossbar. We introduce a number of scheduling algorithms which provide throughput, rate, and delay guarantees. As we shall see, buffered crossbars removes the need for high information complexity and reduces scheduling to a single iteration.

#### 3.1 Background

Figure 3-1 shows a  $3\times3$  buffered crossbar, with line-rate R. To prevent head-of-line blocking, the inputs maintain virtual output queues (VOQs). Fixed length packets wait in the VOQs to be transferred across the switch. Each crosspoint contains a buffer that can hold one cell. The buffer between input i and output j is denoted as  $B_{ij}$ ; when the buffer holds a cell,  $B_{ij} = 1$ , else  $B_{ij} = 0$ .

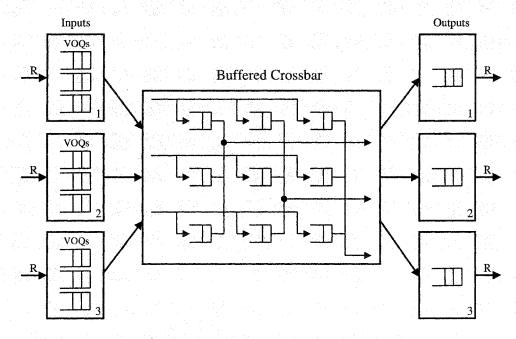

Figure 3-1: The architecture of the buffered crossbar with three ports.

Because the packets are all the same length, time is slotted, with a time slot equal to the time it takes for a cell to arrive on the external line. Internally, the switch runs faster than the external line, and the ratio between the two is the *speedup*. If the switch can remove S cells from each input and transfer S cells to each output in a time slot, then it has a speedup of S. Throughout most of this chapter we will assume that S=2, and so the switch has output queues.

#### 3.1.1 Why use Buffered Crossbars?

Buffered crossbars are interesting because they have simpler scheduling algorithms than an unbuffered crossbar. In an unbuffered crossbar, the scheduler must find a matching between inputs and outputs that does not oversubscribe either. The appeal of a buffered crossbar switch is that its scheduler is much simpler. The scheduler operates in two stages. First, each input (independently and in parallel) picks a cell to place into a crosspoint buffer. Then in the second stage each output (independently and in parallel) picks a crosspoint buffer to take a cell from. The processing

can be distributed to run on each input and output, and so no longer requires a single centralized scheduler. It can be pipelined to run at high speed, making buffered crossbars appealing for high performance switches and routers. At first glance, the architecture seems similar to the DSM and SMS architectures [26, 27] where memory is sandwiched between two switching stages. However, the buffered crossbar architecture is different; it still follows the CIOQ architecture with the caveat that there is a small amount of internal buffering in the crossbar.

Researchers first noticed via simulation that buffered crossbars provide good throughput for admissible uniform traffic with simple algorithms [19, 20, 21, 28]. Simulations also indicated that, with modest speedup, a buffered crossbar can closely approximate fair queueing [22]. In [25], the authors described a mechanism to provide fair allocation and confirmed through simulations that a buffered crossbar can allocate service in a weighted max-min fair manner. Until recently, there were no analytical results on guaranteed throughput to explain or confirm the observations made by simulations.

The first analytical results came in 2001, when Javidi et al. proved that, with uniform traffic, a buffered crossbar can achieve 100% throughput [23]. More recently, Magill et al. proved that a buffered crossbar with a speedup of two can mimic a first-in first-out output queued (FIFO OQ) switch with any arrival traffic pattern [24]. Magill et al. also showed that a buffered crossbar with k cells per crosspoint can mimic a FIFO OQ switch with k strict priorities.

In this chapter, we describe a series of algorithms with a broad class of performance guarantees over and above FIFO and strict priority FIFO emulation. We prove that these algorithms can achieve 100% throughput, can mimic an OQ switch using a weighted round robin scheduler (which gives rate guarantees), and can also achieve delay guarantees. The main benefit of these algorithms is that each input and output makes simple scheduling decisions *independently* and *in parallel*, eliminating the need for a centralized scheduler. Our results show buffered crossbars can greatly simplify the scheduling process.

Of course, simplifying the scheduler comes at the expense of a more complicated crossbar; it now has to hold and maintain  $N^2$  packet buffers. In the past, this would

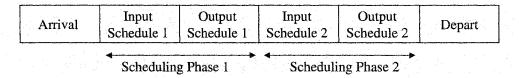

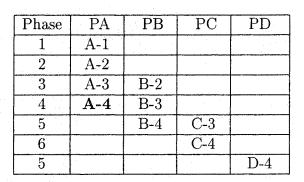

Figure 3-2: The scheduling phases for the buffered crossbar. The exact order of the phases does not matter, but we will use this order to simplify proofs.

have been prohibitively complex; the number of ports and capacity of a crossbar switch used to be limited by the  $N^2$  crosspoints that dominated the chip area (hence the development of multi-stage switch fabrics, such as Clos, Banyan and Omega switches based on smaller crossbar elements). But nowadays, crossbar switches are limited by the number of pins required to get data on and off the chip [29]. Improvements in process technology and reductions in geometries mean that the logic required for  $N^2$  crosspoints is small compared to the size of chip needed for N inputs and N outputs. The chips are pad-limited, with an underutilized die. A buffered crossbar can use the unused die for packet buffers. For example, we believe that in current technology, the  $128 \times 128$  unbuffered crossbar switch reported in [29] could hold  $128^2$  cell buffers.

## 3.2 Achieving 100% throughput with an arbitrary scheduling algorithm

Figure 3-2 shows the scheduling phases in a buffered crossbar with a speedup of two. The two scheduling phases each consists of two parts: input scheduling, and output scheduling. In the input scheduling phase, each input (independently and in parallel) picks a cell to place into an empty crosspoint buffer. In the output scheduling phase, each output (independently and in parallel) picks a cell from a non-empty crosspoint buffer to take from. The key to creating a scheduling algorithm is determining the input and output scheduling policy which decides how inputs and outputs pick cells in the scheduling phases. We will see a number of different policies each of which provides a different scheduling algorithm. The first algorithm we will

consider is the most general. In each scheduling phase, the input picks any non-empty VOQ, and the output picks any non-empty crosspoint.

We will adopt the following notation and definitions. The switch has N ports, and  $VOQ_{ij}$  holds cells at input i destined for output j.  $X_{ij}$  is the occupancy of  $VOQ_{ij}$ , and  $Z_{ij} = X_{ij} + B_{ij}$  is the sum of the number of cells in the VOQ and the corresponding crosspoint. We will assume that all arrivals to input  $i \in 1, 2, 3, ..., N$  are Bernoulli i.i.d. with rate  $\lambda_i$ , and are destined to each output  $j \in 1, 2, 3, ...N$  with probability  $\lambda_{ij}$ . We will denote the arrival matrix as  $A \equiv [\lambda_{ij}]$ , where for all i, j,

$$\lambda_i = \sum_{j=1}^{N} \lambda_{ij}, \lambda_j = \sum_{i=1}^{N} \lambda_{ij}, \lambda_{ij} \ge 0$$

In what follows, we will show that the buffered crossbar can give 100% throughput. The result is quite strong in the sense that it holds for any arbitrary work-conserving input and output scheduling policy with a speedup of two. In other words, each input i can choose to serve any non-empty VOQ for which  $B_{ij} = 0$ , and each output j can choose to serve any crosspoint for which  $B_{ij} = 1$ .

**Theorem 8** (Sufficiency) A buffered crossbar can achieve 100% throughput with speedup two for any Bernoulli i.i.d. admissible traffic.

*Proof:* We describe an intuition of the proof. The main proof appears in Appendix D.

For each  $VOQ_{ij}$ , let  $C_{ij}$  denote the sum of the cells waiting at input i and the cells waiting at all inputs destined to output j (including cells in the crosspoint for output j),

$$C_{ij} = \sum_{k} X_{ik} + \sum_{k} (X_{kj} + B_{kj})$$

(3.1)

It is easy to see that when  $VOQ_{ij}$  is non-empty (i.e.,  $X_{ij} > 0$ ), then  $C_{ij}$  decreases in every scheduling phase. There are two cases:

<sup>&</sup>lt;sup>1</sup>We will see later that other queueing structures are useful and that it is not necessary to place cells in VOQs.

- Case 1:  $B_{ij} = 1$ . Output j will receive one cell from the buffers destined to it and  $\sum_{k} (X_{kj} + B_{kj})$  will decrease by one.

- Case 2:  $B_{ij} = 0$ . Input i will send one cell from its VOQs to a crosspoint, and  $\sum_{k} X_{ik}$  will decrease by one.<sup>2</sup>

With S=2,  $C_{ij}$  will decrease by two per time slot. When the inputs and outputs are not oversubscribed, the expected increase in  $C_{ij}$  is strictly less than two per time slot. So the expected change in  $C_{ij}$  is negative over the time slot, and this means that the expected value of  $C_{ij}$  is bounded. This in turn implies that the expected value of  $X_{ij}$  is bounded and the buffered crossbar has 100% throughput.

#### 3.3 Counting Method with a Buffered Crossbar

We will now show how the buffered crossbar can mimic an OQ switch in a simple distributed manner where each input and output makes decisions independently and in parallel.

In chapter 2, a counting method is introduced to show that a CIOQ switch using a traditional unbuffered crossbar with a speedup of two can mimic a PIFO OQ switch. As a reminder, the counting method requires that in each scheduling phase, at least one of the following conditions for each cell c is satisfied: (1) cell c is transferred from the input side, (2) a cell that is ahead of cell c in its input priority list is transferred from the input side, or (3) a cell that is ahead of cell c in its output priority list is transferred to the output side.

It is proved that meeting the conditions of the counting method ensured that the slackness of a cell increased by at least one in each scheduling phase, which is essential in proving that the slackness of any cell is always non-negative. However, the scheduling algorithms require a *stable marriage algorithm* to meet the conditions of the counting method. The solution requires up to at least N iterations of the

<sup>&</sup>lt;sup>2</sup>If a cell from  $VOQ_{ij}$  is sent to crosspoint  $B_{ij}$ , then  $\sum_{k}(X_{kj}+B_{kj})$  stays the same at the end of the input scheduling phase since  $X_{ij}$  decreases by one and  $B_{ij}$  increases by one. In the output schedule, Case 1 applies and  $C_{ij}$  will further decrease by one. As a result, if a cell from  $VOQ_{ij}$  is sent to crosspoint  $B_{ij}$ , then  $C_{ij}$  decreases by two in that scheduling phase.

stable marriage algorithm for a switch with N ports, making them too complex to implement for fast switches with large number of ports.

In order to ensure that the slackness of a cell increases by at least one in each scheduling phase for a buffered crossbar, the input and output scheduling policies must carefully be selected to guarantee that the conditions of the counting method are met. The input scheduling policy gives preference to cells based on the input priority list. Similarly, the output scheduling policy gives preference to cells based on the output priority list. Since the output priority list is ordered based on departure order, preference is given to cells with an earlier departure order.

However, the buffered crossbar has an additional requirement to meet the conditions of the counting method. The input priority list must also be arranged so cells destined to the same output are ordered based on departure order. Specifically, cells to the same output with an earlier departure order must have a higher priority. Cells to different outputs can still be ordered in any way. This requirement is necessary to ensure that, in the output scheduling phase, the cell selected has the earliest departure order of the cells stored in the input queues corresponding to the non-empty crosspoint, as can be seen in the following example.

Let cells a, b, and c all be destined to output j. Cell a is stored in input queue  $i_1$ , cell b is stored in input queue  $i_2$ , cell c is stored in crosspoint  $B_{i_1j}$ , and no other cells are destined to output j at time t. The departure order is  $t_a < t_b < t_c$  for cells a, b, and c respectively. In the input scheduling phase, input  $i_1$  does not select cell a since cell c is already in the crosspoint  $B_{i_1j}$ , and input  $i_2$  selects cell b. In the output scheduling phase, cell b is selected since it has an earlier departure order than cell c. As a result, the conditions of the counting method is not met for cell a since cell b, which has a later departure order, does not have a higher priority than cell a in the output priority list. This occurred because at some point in time cell c was incorrectly given a higher priority than cell a in the input priority list. This motivates the following "Group By Virtual Output Queue" insertion policy previously described in Chapter 2.

#### **GBVOQ** Insertion Policy:

1. When a cell arrives to a non-empty VOQ, the cell is inserted in the input priority

list just behind the last cell belonging to the same VOQ. This ensures that cells destined to the same output are ordered based on departure order.

2. When a cell arrives to an empty VOQ, the cell is inserted at the head of the input priority list.

We will now prove in the following lemma that the buffered crossbar can satisfy the conditions of the counting method.

**Lemma 9** The slackness L(c) of a cell c decreases by at least one in each scheduling phase.

*Proof:* Let's assume that cell c belongs to  $VOQ_{ij}$ . There are two cases to consider in a scheduling phase.

- Case 1: If  $B_{ij} = 0$ , then we know that in the input scheduling phase, a cell will be transferred from input i to one of the buffers  $B_{i*}$ . If cell c is transferred to  $B_{ij}$ , then we no longer need to consider it.<sup>3</sup> If a different cell is transferred to its crosspoint buffer, the cell would belong to c's input thread, and IT(c) will decrease by one.

- Case 2: If  $B_{ij} = 1$ , then a cell will be transferred from one of the crosspoints  $B_{*j}$  to output j in the output scheduling phase. By definition of the GBVOQ insertion policy the cell in crosspoint  $B_{ij}$  has an earlier departure order than cell c. Since the output scheduling policy selects the non-empty crosspoint that contains the cell with the earliest departure order, OC(c) increases by one.

Therefore, L(c) increases by at least one per scheduling phase.

The counting method using the GBVOQ insertion policy can be applied trivially to show that a buffered crossbar can mimic a restricted PIFO OQ switch, i.e., a PIFO OQ switch with the restriction that cells from an input/output pair depart the switch in the order they arrive. This restricted policy includes output link schedulers which are fair across all inputs, i.e., provide rate guarantees between each input/output pair.

<sup>&</sup>lt;sup>3</sup>If a cell is transferred to the crosspoint then it is available for selection in the output scheduling phase and can be placed on the output line whenever necessary.

**Theorem 10** (Sufficiency) A buffered crossbar with a speedup of two can mimic the restricted PIFO OQ switch, regardless of the incoming traffic pattern.

Proof: See Appendix E.1.

#### 3.4 Rate Guarantees with a Buffered Crosbar

Our goal is to find a way for a buffered crossbar to provide a pre-determined and guaranteed rate for each flow passing through the switch. In an OQ switch, this is straightforward to do with, e.g., a weighted round-robin (WRR) scheduler. A WRR scheduler serves each flow queue in turn in round-robin order, giving service to each queue in proportion to the weight assigned to it. If a queue is empty, it is skipped and not served. It is well known that — when packets are all of equal length — WRR gives each flow a rate in proportion to its weight, and hence can give a minimum rate guarantee to each flow. Furthermore, if the arrival processes are suitably constrained (e.g., by leaky buckets), then the delay of each packet through the switch can be bounded [5].

One approach to proving that a buffered crossbar can provide rate guarantees would be to show that the buffered crossbar can mimic a PIFO OQ switch. Then, because WRR is a special case of PIFO, we can conclude that the buffered crossbar can support WRR and provide rate guarantees just as an OQ switch can. But as we will see in the next section, it is harder for a buffered crossbar to mimic a PIFO OQ switch.

So instead, we are going to start by solving an easier problem by considering a restricted PIFO OQ switch. In what follows, a flow is defined to be those cells between a specific input/output pair. We will consider a WRR OQ switch that serves these flows in WRR order and try to mimic the same behavior with a buffered crossbar.

In the restricted WRR OQ switch, each arriving cell is assigned a virtual finishing time by the WRR scheduler. Reviewing the way a WRR scheduler works, let us consider the cells at just one output. The  $k^{th}$  cell from input i is assigned virtual

finishing time  $F_i^k$ , where

$$F_i^k = \max\{F_i^{k-1}, V(a_i^k)\} + \frac{1}{\phi_i}.$$

$a_i^k$  is the arrival time of the  $k^{th}$  cell from input i to that output, V(t) is the virtual time (round number) at time t, and  $\phi_i$  is the weight assigned to input i. When the output line is free, the WRR scheduler serves the cell with the smallest virtual finish time.